晶片是用來幹嘛的?為什麼日常生活中會用到晶片呢?晶片這麼重要嗎?晶圓又是什麼呢?

在過去,需要將電晶體、二極體、電阻、電容等電子元件焊接成電路,並將這個能執行簡單邏輯運算的電路裝置在電子產品上,才能夠讓電子產品順利運作,然而手工焊接不僅成本高且耗時,效果也不理想。後來德州儀器的工程師 – 傑克·基爾比,便想到如果能夠事先設計好電路圖,然後照電路圖將所有電子元件整合在矽晶元上,便能解決手工焊接的難題,而這就是全世界第一個「積體電路」也就是我們常聽到的IC(Integrated Circuit)的由來。

積體電路發明後,技術也開始高速發展,一個晶片從原本僅能塞不到五個電晶體,到後來可以塞下數億個電晶體。而電晶體縮得越小,除了更低的能耗、延遲以及更高的效能外,也讓晶片隨之縮小,電子產品也能越來越小。如今這些優點正反應在電子產品上,讓生活越來越方便。

編按 2025/06/18 更新:TrendForce 報告指出,在美國實施對等關稅政策以及中國大陸推出消費補貼帶來提前拉貨效應,緩解傳統第一季的淡季影響,讓 2025 年第一季全球晶圓代工產業營收僅微幅季減5.4%。台積電 TSMC 仍以 67.6% 的市占率穩坐產業龍頭,三星 Samsung Foundry 則以 7.7% 次之,接著分別為中芯國際 SMIC(6.0%)、聯電 UMC(4.7%)、格羅方德 GlobalFoundries(4.2%)的占比排序。

同時值得注意的是,另有華虹集團及合肥晶合兩家公司排進前十,讓陸系晶圓廠市占率達 9.7 %,中國晶圓代工業者的市占正在持續提升。

晶圓代工是什麼?

晶圓代工(Foundry)是半導體產業的一種商業模式,指接受其他無廠半導體公司(Fabless)委託、專門從事晶圓成品的加工而製造積體電路,並不自行從事產品設計與後端銷售。下面帶你認識晶圓代工的流程。

晶圓代工流程一:矽晶圓生產

晶片最偉大的貢獻,莫過於將原本僅能執行 0 和 1 的邏輯運算(註)的電晶體,集合在一起形成具有強大處理能力的運算中樞,而連結這些電晶體的基板就是「矽」這個元素。

之所以會選擇「矽」作為 IC 的主要原料,是因為矽在自然界中屬於「半導體」,也就是導電性介於導體與絕緣體的存在,可以藉由加入雜質,來調整半導體的導電性,進而控制電流是否流通,達到訊號切換的功能,換句話說就是讓晶片能夠順利執行 0 和 1 的運算,而能操控電子產品。

矽晶圓的製造流程簡化來說就是將「矽」加工至可用來放置電子元件的「矽晶圓 」

矽晶圓製作流程

純化 : 矽的前身是石英砂,裡面含有許多雜質,因此需要將其純化,主要方式為將石英砂加入碳並加熱還原成冶金級矽,隨後將其丟入反應爐中與氯化氫以及氫氣反應形成多晶矽。

拉晶 : 將多晶矽置入單晶爐中,透過加熱處理、接入晶種(註1)後,就可以從中拉出半導體產業所需的「單晶矽柱」(矽晶柱),上面會有可擺放電晶體的「矽晶格」,也因此矽晶柱的品質掌控對於晶圓廠來說至關重要,拉晶的速度、溫度的控制等等因子都有可能大大影響到最後的生產品質,而矽晶柱直徑越大,拉晶也就越難。(註 2)

註1 : 這邊的晶種指的是一小塊單晶矽,透過將晶種與熔融物接觸並冷卻凝固,藉此形成大晶體,目的是讓晶圓的原子排列能與晶種相同。

註2 : 單晶矽與多晶矽的區別 : 當矽原子以金剛石晶格排列成許多晶核時,如果各個晶核的晶面取向相同,則稱為單晶矽,如果晶面取向不同,則稱為多晶矽,在電學性質表現上,單晶矽優於多晶矽,因此在半導體產業中多採用單晶矽作為主要原料。

到這邊為止,安置電子元件的基板 – 矽晶圓便完成了,而我們常在新聞中看到的 8 吋晶圓廠、12 吋晶圓廠,指的其實就是矽晶圓的直徑,不過,為什麼要特地分成 8 吋、12 吋或是 X 吋呢?

8吋晶圓 vs 12吋晶圓

其實關鍵就在於「生產成本」。簡單的數學運算就可知道,一片12吋晶圓的表面積是一片8吋晶圓的2.25倍,也就是說在相同良率下,12吋晶圓廠的生產效率會是8吋晶圓廠的2.25倍,因此只要兩種晶圓尺寸的生產成本差距在2.25倍以下的話,生產12吋晶圓便會比生產8吋晶圓來的有優勢,故生產12吋晶圓其實是較為先進的技術。

12 吋晶圓廠較有生產效率,為什麼還要保留 8 吋晶圓廠?

前面提到,12 吋晶圓廠的產量平均來說會是 8 吋晶圓廠的兩倍多,因此在產能滿載的前提下,12 吋廠比較符合成本效益,然而對於某些客戶集中在利基市場的廠商來說,不見得有足夠的出貨量去支撐12 吋廠帶來的額外產能,因此對這些廠商來說,也就沒必要花更多的資金投資技術門檻更高的 12 吋廠。

8 吋晶圓供不應求?

前面提到,某些產品市場規模不大,因此透過 8 吋或 6 吋晶圓廠來生產較有效率,相對的某些產品市場規模較大,因此產線通常都會分佈在 12 吋晶圓廠。過去 12 吋晶圓廠主要拿來生產智慧型手機、筆記型電腦等有高階運算需求的晶片,另一方面 6 吋、8 吋晶圓廠則是用於生產物聯網、車用元件等運算能力要求度不高的晶片。

由於過去 12 吋晶圓廠為市場主流,因此部分晶圓設備廠已經停止生產 8 吋晶圓廠的設備,而直接蓋新的 8 吋廠又需要龐大的資金,對於大部分業者來說難以負荷。外加隨著 5G 逐漸普及,物聯網相關的晶片需求提升,因此 8 吋晶圓市場近期才會供不應求。

| 資料來源 : 君安投顧、金融家月刊 | |

| 各尺寸晶圓主要應用產品類別 | |

| 晶圓尺寸 | 應用產品 |

| 12吋 | 邏輯IC、NAND/NOR Flash、DRAM、微控制器 |

| 8吋 | 類比IC、NAND/NOR Flash、離散元件、感測器 |

| 6吋 | 離散元件、感測器 |

晶圓代工流程二:積體電路製造

回到 IC 製造的工作流程介紹,前面提及過去製作電路的方法,是將所有的電子元件手工連接起來,而相較之下積體電路的優勢,就在於他是直接依照設計好的電路圖,一口氣將所有電子元件整合在一起。因此有個一致的標準,生產起來容易許多。

這兩種電路製作模式的關鍵差異來自於「光學原理」。

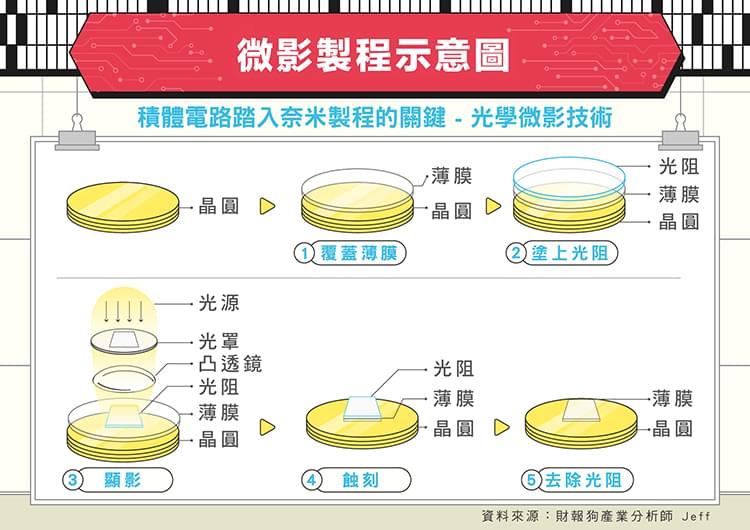

簡單來說,積體電路製造就是將從 IC 設計廠拿到的「電路設計圖」透過光學成像的原理轉移到「矽晶圓」上,最後依照設計圖架構,在矽晶元上集成化所需的電子元件 :

- 步驟 1 – 鍍上薄膜 : 於矽晶片表面鍍上氧化層(或金屬)。

- 步驟 2 – 塗上光阻 : 於薄膜表面塗上光阻劑,該光阻劑曝光後化學結構會改變,變的相當易溶。

- 步驟 3 – 顯影 : 透過紫外光與凸透鏡的聚光效果,將光罩上的電路圖縮小並投影在光阻上。

- 步驟 4 – 蝕刻 : 透過特殊化學溶液將被紫外光照射的光阻沖洗掉,接著再透過另一種化學溶液將步驟1的薄膜沖洗掉。

- 步驟5 – 光阻去除 : 接著最後一樣以化學溶液將光阻去除。

註 : 實際過程相當複雜,需要堆疊許多不同材質的薄膜在特定的位置,因此需要好幾十層的光罩並且不斷重複上述步驟才能完成光刻製程,其他關於晶圓清洗、烘烤等步驟限於篇幅的關係,無法詳細陳述。

註 : 實際過程相當複雜,需要堆疊許多不同材質的薄膜在特定的位置,因此需要好幾十層的光罩並且不斷重複上述步驟才能完成光刻製程,其他關於晶圓清洗、烘烤等步驟限於篇幅的關係,無法詳細陳述。

在光刻製程結束後,緊接著就是注入雜質(磷原子與硼原子)到矽晶片(半導體)中控制其導電性,至此,構成積體電路所需的電晶體及相關的元件便已依照設計好的電路圖在矽晶片上集成完畢,最後將銅倒入溝槽中形成電子接線,將數億個電晶體串接起來後,近半個世紀以來不斷推動科技進步的基石 – 積體電路便就此完成。

晶圓代工廠如何突破物理極限提升光刻技術?

相信有在關注台積電的投資人多少會看過跟上述類似的新聞,不過在探討什麼是摩爾定律、EUV等專有名詞前,必須先了解光刻技術如何演進。

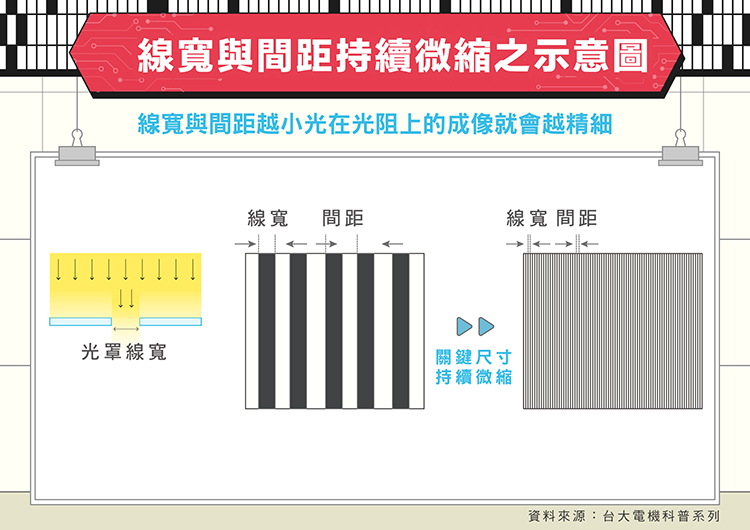

R = k1 x NA 是光學微影的分辨率公式,要想要有更好的成像品質,就必須要想辦法提升分辨率,上述公式中,R代表至多可以曝出多小的線寬,越小則代表越精細、分辨率越高,能夠執行越精細的光刻作業,代表光在真空中的波長,NA代表成像系統的數值孔徑,k1則是一係數(受到許多製程相關因子影響)。

所以根據上述公式,要想提高分辨率,主要可以透過降低光源波長或是提高成像系統的數值孔徑(註)來達成。

註 : 數值孔徑(NA)沒有單位。是用以衡量一個光學系統(鏡頭)能夠收集的光的角度範圍。

EUV是什麼?

EUV微影技術的落實延續了摩爾定律的壽命,這裡的 EUV 指的其實是一種紫外光源,跟過去光刻技術所採用的光源比起來,EUV的波長更短,因此有助於大幅提高分辨率。

| 光源種類 | 光源波長 |

| 紫外光(UV) | 400 奈米以下 |

| 深紫外光(DUV) | 300 奈米以下 |

| 極紫外光(EUV) | 100 奈米以下 |

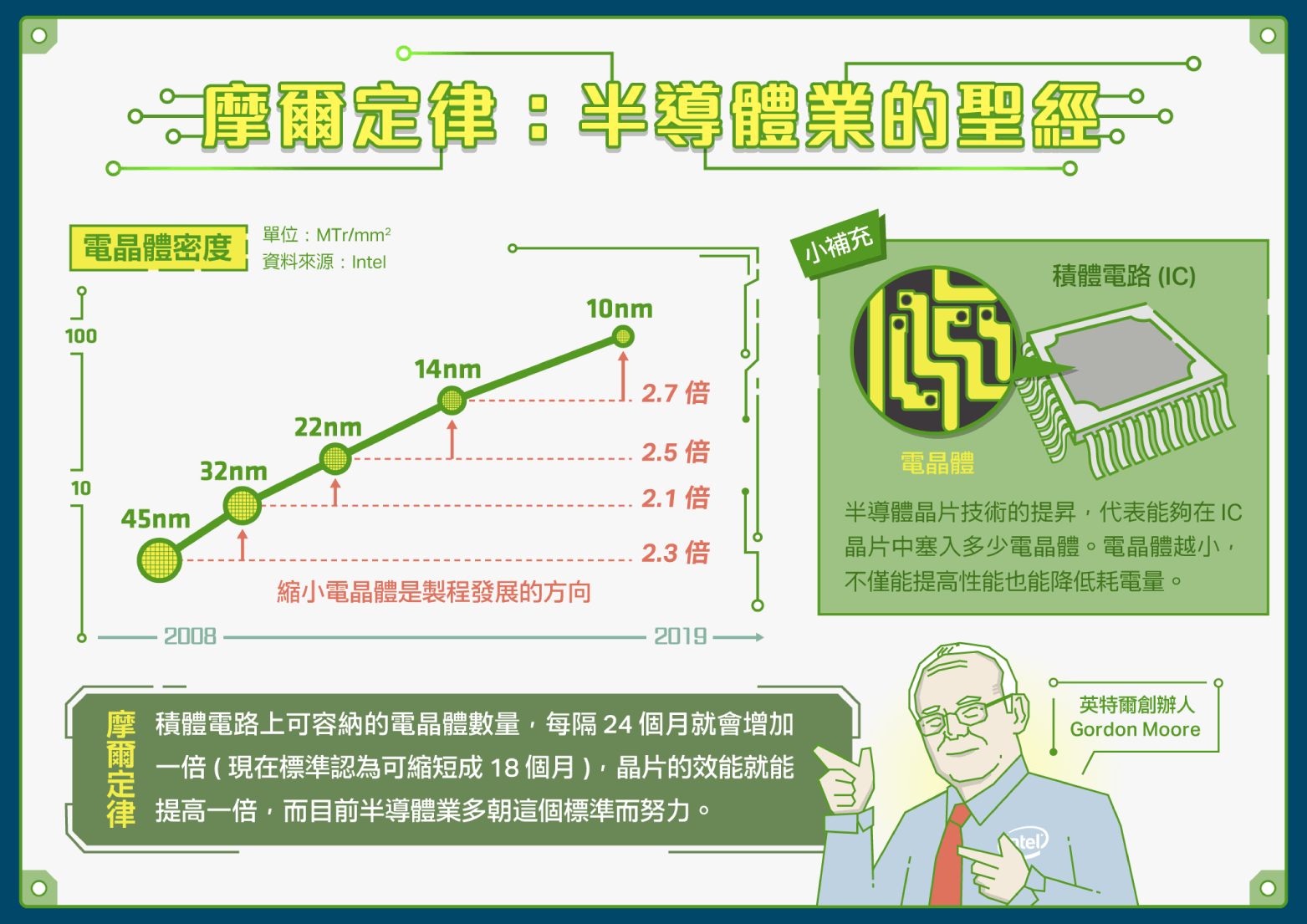

摩爾定律是什麼?

摩爾定律指的是積體電路上可容納的電晶體數目,約每隔十八個月到兩年增加一倍、性能也提升一倍,所以與其說是“定律”,其實它更像是一個用來描述積體電路產業演進軌跡的指標,而近幾年許多新聞媒體之所以會認為摩爾定律快走到盡頭,主要就是因為過去採用DUV光源的光刻技術在分辨率的提升上已經到達極限,換句話說就是媒體認為晶圓代工廠已經沒有辦法提供具有更高效能的晶片,這對晶圓代工廠甚至是對整個科技產業來說都會是相當大的衝擊,也幸虧EUV微影技術的成功,才讓摩爾定律得以延續。

💡延伸閱讀>>>摩爾定律是什麼?還有類摩爾定律?自我實現的摩爾定律!

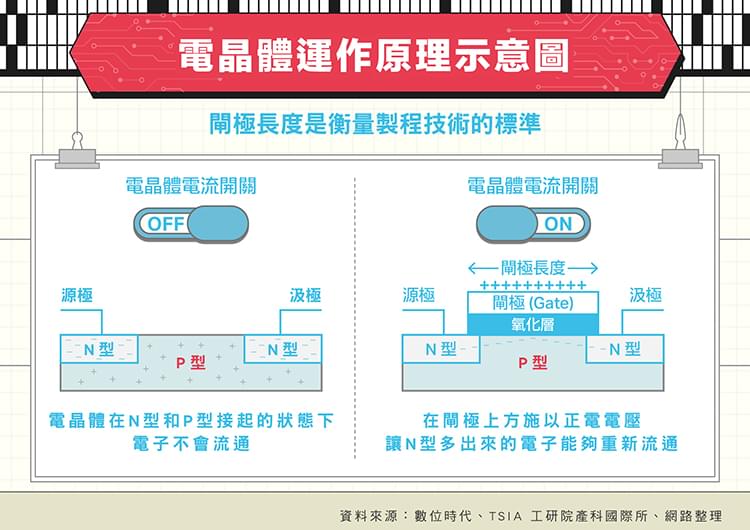

晶圓幾奈米是什麼意思?

奈米是一公尺的負 9 次方,也就是頭髮厚度的 10 萬分之一。而新聞上看到的「XX 奈米」,則是指晶片上電晶體控制電流通過的「閘極長度」,長度越小,電晶體就越小,能塞進晶片的電晶體數量就越多,設備的效能也會相應提升。

而隨著技術精進,奈米製程也逐步縮小。就如前所述,網路越來越快,也因此需要更先進、更精密的晶片。這,就讓台積電「純代工」的優勢逐漸顯現。

【延伸閱讀】