傳統個別封裝

傳統個別封裝技術是將處理器(CPU)、記憶體、邏輯元件、類比元件等「數個」功能不同的晶片(Chip),分別封裝成「數個」不同的積體電路(IC),再分別焊接在一塊印刷電路板(PCB)上。

以個人電腦的主機板為例,處理器是一個積體電路,記憶體是另外一個積體電路,北橋晶片和南橋晶片是另外兩個積體電路…依此類推,所有的積體電路都焊接在一塊印刷電路板上,才能互相配合進行運算的工作,這種方式會使整個系統的體積較大、成本較高,電訊號必須在印刷電路板上傳送較長的距離才能進行運算,造成耗電量大,而且運算速度慢,系統功能較差。

系統單晶片(SoC:System on a Chip)

將數個功能不同的晶片,整合成「一個」具有完整功能的晶片,再封裝成「一個」積體電路,稱為「系統單晶片(SoC:System on a Chip)」。

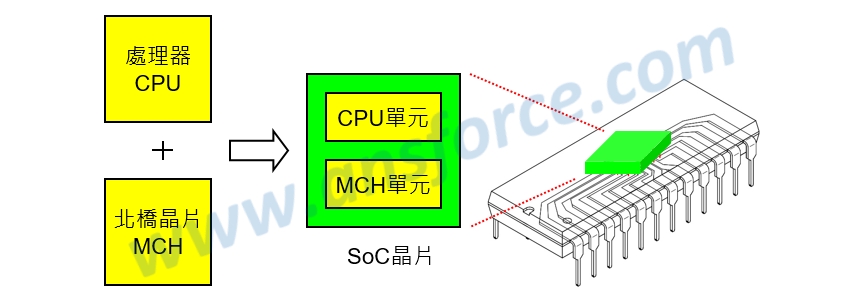

例如:將處理器變成「CPU 單元」,北橋晶片變成「MCH 單元」,整合在同一個光罩上,製作成一個晶片,如<圖一>所示,目前 Intel(INTC-US)公司就是朝向這個方向努力,以縮小筆記型電腦的體積。

圖一、系統單晶片示意圖

系統單晶片的優點

➤減少體積:以印刷電路板組合數個不同功能的積體電路,體積較大;如果整合成一個 SoC 晶片,則體積變小。

➤減少成本:需要封裝測試多顆積體電路,成本較高;如果整合成一個 SoC 晶片,只需要封裝測試一顆積體電路,成本較低。

➤降低耗電量同時提高運算速度:以印刷電路板組合數個不同功能的積體電路,電訊號必須在印刷電路板上傳送較長的距離才能進行運算,耗電量較高,運算速度較慢;如果整合成一個 SoC 晶片,電訊號在同一個積體電路內傳送較短的距離就能進行運算,耗電量較低,運算速度較快。

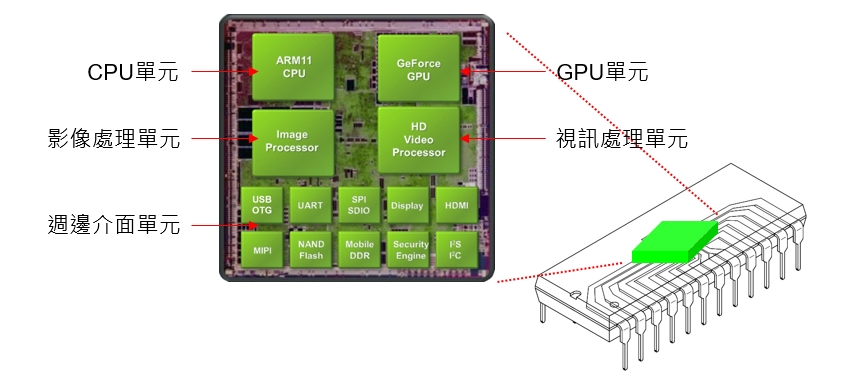

➤提升系統功能:將不同功能的積體電路整合成一個 SoC 晶片,體積較小,可以整合更多的「功能單元」,形成功能更強大的晶片。目前已經有許多非常成功的 SoC 晶片在市場上銷售,<圖二>是 Nvidia(NVDA-US)公司設計的 Tegra 650 多媒體系統單晶片,結合中央處理器(CPU)、圖形處理器(GPU)、影像處理器(Image/Video processor)、其他周邊介面等功能單元。

圖二、Nvidia Tegra 650系統單晶片(資料來源:www.nvidia.com)

系統單晶片的挑戰

由於 SoC 晶片的設計與驗證必須與半導體製造技術配合,再加上必須具備完整的混合訊號、數位與類比、低頻與高頻、記憶體等相關的智慧財產權(IP)產業互相配合,因此系統單晶片的設計仍然有許多困難極待克服,系統單晶片的設計瓶頸包括:

➤製造瓶頸:不同功能單元的製程技術不同,要同時製作在矽晶片上非常困難,數位電路的整合比較容易,數位與類比電路兩者要整合在一起就比較困難。

➤封裝瓶頸:SoC 晶片功能強大,工作頻率增加,必定會造成線路的訊號產生雜訊互相干擾,必須使用覆晶封裝、錫球封裝、晶圓級封裝等技術加以克服。

➤測試瓶頸:測試機台必須同時具備多種數位與類比訊號的測試功能,因此必須發展多功能單一機型的測試機台,同時測試不同功能的 SoC 晶片。

【請注意】上述內容經過適當簡化以適合大眾閱讀,與產業現狀可能會有差異,若您是這個領域的專家想要提供意見,請自行聯絡作者;若有產業與技術問題請參與社群討論。

《知識力》授權轉載

【延伸閱讀】